Important Dates

Call for Papers

Organizing Committee

Program Committee

Author Information

Paper Submission

Camera Ready Submission

Technical Program

Conference Panel

Keynote Speakers

Conference Registration

Venue

Travel & Hotel

Sponsors

Contact Us

Past Conferences

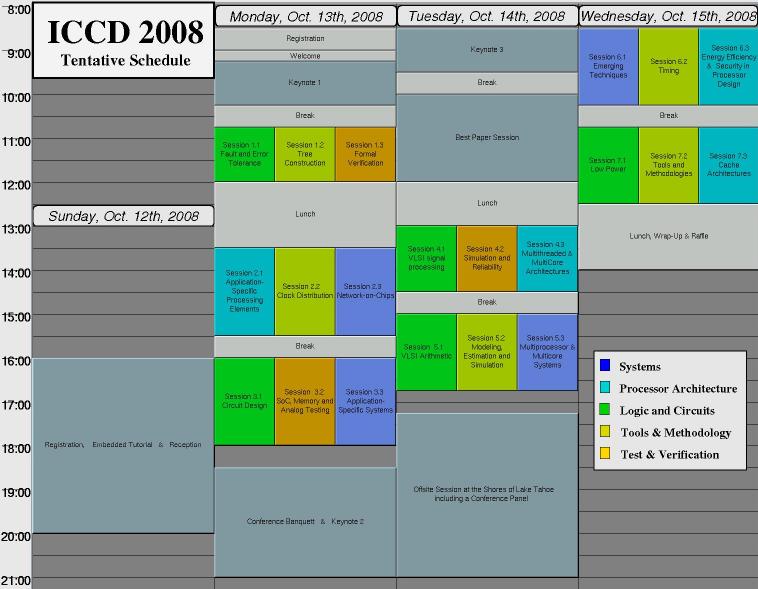

ICCD 2008 Schedule

The full resolution diagram of the ICCD 2008 Schedule can be found here.

ICCD 2008 Schedule Listed by Time

Check the diagram for the color codes.

Embedded tutorial

Sunday 10/12/08

Organized by Bhanu Kapoor (Mimasic), Shankar Hemmady and Prapanna Tiwari (Synopsys), Kaushik Roy (Purdue), Manuel D.Abreu (SanDisk Corp).

The topic is SoC Power Management Verification.

Keynote I

Monday 10/13/08, 9:20-10:30

Towards More Sustainable Computer Design

Fred Chong

Director, Greenscale Center for Energy-Efficient Computing

University of California at Santa Barbara

Session I

Monday 10/13/08, 10:45-12:00

Logic and Circuits Track

Session 1.1 Fault and error tolerance (75 min)

Session chair: Bart Zeydel, Plato Networks

Werner Friesenbichler, Thomas Panhofer and Martin Delvai.

Fault Tolerant Four-State Logic by Using Self-Healing Cells

Nasir Mohyuddin, Ehsan Pakbaznia and Massoud Pedram.

Probabilistic Error Propagation in a Logic Circuit Using the Boolean Difference Calculus

Rajesh Garg and Sunil Khatri.

A Novel, Highly SEU Tolerant Digital Circuit Design Approach

EDA Track

Session 1.2 Tree Construction (75 min)

Session chair: TBD

Iris Hui-Ru Jiang and Ming-Hua Wu.

Power-State-Aware Buffered Tree Construction

Christian Fobel and Gary Grewal.

An efficient, multi-processor graph-based Steiner tree heuristic for the global routing of macro cells

Iris Hui-Ru Jiang and Yen-Ting Yu.

Configurable Rectilinear Steiner Tree Construction for SoC and Nano Technologies

Verification and Test Track

Session 1.3 Formal Verification (75 min)

Session chair: TBD

Fabricio Andrade, Leandro Silva and Antonio Fernandes.

Improving SAT-Based Combinational Equivalence Checking Through Circuit Preprocessing

Xueqi Cheng and Michael Hsiao.

Ant Colony Optimization Directed Program Abstraction for Software Bounded Model Checking

Bernd Becker, Marc Herbstritt, Natalia Kalinnik, Matthew Lewis, Juri Lichtner, Tobias Nopper and Ralf Wimmer.

Propositional Approximations for Bounded Model Checking of Partial Designs

Session II

Monday 10/13/08, 13:30-15:35

Processor Architecture Track

Session 2.1 Application-Specific Processing Elements (125 min)

Session chair: Jim Bondi, TI

Jeff Pool, Anselmo Lastra and Montek Singh.

Energy-Precision Tradeoffs in Mobile Graphics Processing Units

Pankaj Bhagawat, Rajballav Dash and Gwan Choi.

Dynamically Reconfigurable Soft Output MIMO Detector

Alberto Antonio Del Barrio Garcia, Maria del Carmen Molina, Jose Manuel Mendias, Esther Andres, Roman Hermida and Francisco Tirado.

Applying branch prediction techniques to implement functional units

(Short presentation)

Atif Hashmi and Mikko Lipasti.

Accelerating Search and Recognition with a TCAM Functional Unit

Brian Hickmann, Michael Schulte and Mark Erle.

Improved Combined Binary/Decimal Fixed-Point Multipliers

(Short presentation)

Jose-Luis Sanchez, Higinio Mora Mora, Jeronimo Mora-Pascual and Antonio Jimeno.

Architecture Implementation of an improved Decimal CORDIC Method

EDA Track

Session 2.2 Clock Distribution (125 min)

Session chair: Elaheh Bozorgzadeh, The University of California at Irvine

Aida Todri and Malgorzata Marek-Sadowska.

A Study of Reliability Issues in Clock Distribution Networks

Chunchen Liu, Junjie Su and Yiyu Shi.

Temperature Aware Clock Tree Synthesis Considering Spatiotemporal Hot Spot Correlations

Vinayak Honkote and Baris Taskin.

Custom Rotary Clock Router

Keisuke Inoue, Mineo Kaneko and Tsuyoshi Iwagaki.

Safe Clocking Register Assignment in Datapath Synthesis

Weixiang Shen, Yici Cai, Xianlong Hong and Jiang Hu.

Gate Planning During Placement for Gated Clock Network

Computer Systems Track

Session 2.3 Network-on-Chips (125 min)

Session chair: TBD

Rohit Sunkam Ramanujam and Bill Lin.

Near-Optimal Oblivious Routing on Three-Dimensional Mesh Networks

Shan Yan and Bill Lin.

Design of Application-Specific 3D Networks-on-Chip Architectures

Mohammadreza Aghajani, Arash Tavakkol, Mohammad Sadegh Talebi and Ahmad Khonsari.

Mathematical analysis of buffer sizing for on-chip interconnection networks under multimedia traffic

Karthikeyan Sabhanatarajan and Ann Gordon-Ross.

A Resource Efficient Content Inspection System for Next Generation Smart NICs

Chen-Ling Chou and Radu Marculescu.

Contention-aware Application Mapping for Networks-on-Chip Communication Architectures

(conditional accept)

Session III

Monday 10/13/08, 16:00-18:05

Logic and Circuits Track

Session 3.1 Circuit design (125 minutes)

Session chair: Nestoras Tzartzanis, Fujitsu

Logic and Circuits Track

Session 3.1 Circuit design (125 minutes)

Session chair: Nestoras Tzartzanis, Fujitsu

Kaijian Shi.

Area and Power-Delay Efficient State Retention Pulse-Triggered Flip-Flops with Scan and Reset Capabilities

Baker Mohammad, Stephen Bijansky, Adnan Aziz and Jacob Abraham.

Adaptive SRAM-based Memory for Low Power and High Yield

Yulei Zhang, Ling Zhang, Akira Tsuchiya, Masanori Hashimoto and Chung-Kuan Cheng.

On-Chip High Performance Signaling using Passive Compensation

Michael Pehl, Tobias Massier, Helmut Graeb and Ulf Schlichtmann.

A random and pseudo-gradient approach for analog circuit sizing with non-uniformly discretized parameters

(Short presentation)

Hamed Abrishami, safar hatami and Massoud Pedram.

Characterization and Design of Sequential Elements to Combat Soft Errors

(Short presentation)

Ramakrishnan Krishnan, Vijaykrishnan Narayanan and Yuan Xie.

Comparative Analysis of NBTI Effects on Low Power and High Performance Flip-Flops

Verification and Test Track

Session 3.2 SoC, Memory and Analog Testing (125 min)

Session chair: TBD

Jason Lee and Rabi Mahapatra.

In-Field NoC-Based SoC Testing with Distributed Test Vector Storage

Xiaoxia Wu, Yibo Chen, Krish Chakrabarty and yuan xie.

Test-Access Mechanism Optimization for Core-Based Three-Dimensional SOCs

Jae Chul Cha and Sandeep Gupta.

Characterization of Granularity and Redundancy for SRAMs for Optimal Yield/Area

Ender YILMAZ and Sule Ozev.

Dynamic Test Scheduling for Analog Circuits for Improved Test Quality

Mingjing Chen and Alex Orailoglu.

Test Cost Minimization through Adaptive Test Development

Computer Systems Track

Session 3.3 Application-Specific Systems (125 min)

Session chair: Michael Gschwind

Fei Xia, Yong Dou and Jiaqing Xu.

Fine-grained Parallel Application Specific Computing for RNA Secondary Structure Predication on FPGA

(conditional accept)

Zhibin Xiao and Bevan Baas.

A High-Performance Parallel H.264 CAVLC Encoder on a Fine-Grained Many-core System

Sebastien Fontaine, Sylvain Goyette, J.M. Pierre Langlois and Guy Bois.

Acceleration of a Target Tracking Algorithm Using an Application Specific Instruction set Processor

Amirhossein Gholamipour, Eli Bozorgzadeh and Lichun Bao.

Seamless Sequence of Software Defined Radio Designs through Hardware Reconfigurability of FPGAs

(Short presentation)

Marc-Andre Daigneault, Pierre Langlois and Jean-Pierre David.

Application Specific Instruction Set Processor Specialized for Block Motion Estimation

(Short presentation)

Dong Ye, Aravind Pavuluri, Brian Tsang, Bob Rychlik and Steven Woo.

Prototyping a Hybrid Main Memory System Using a Virtual Machine Monitor

Conference Banquet and Keynote II

Monday 10/13/08, 18:30-20:00

Green Computing: Big Challenges and Little Solutions

Chris Rowen

Chief Technology Officer

Tensilica

Keynote III

Tuesday 10/14/08, 8:30-9:30

Lean IT: Lead or Die

Christian Belady

Principal Power and Cooling Architect

Microsoft

Best Paper Session

Tuesday 10/14/08, 9:45-11:50

Session chairs: Peter-Michael Seidel, AMD

Georgi Gaydadjiev, TU Delft

Computer Systems Track

Eren Kursun and Chen-Yong Cher.

Variation-aware Thermal Characterization and Management of Multi-core Architectures

Processor Architecture Track

Venkatesan Packirisamy, Antonia Zhai and Pen-Chung Yew.

Performance and Power Comparison of Thread-Level Speculation in SMT and CMP Architectures

Logic and Circuits Track

David Bol, Renaud Ambroise, Denis Flandre and Jean-Didier Legat.

Analysis and Minimization of Practical Energy in 45nm Subthreshold Logic Circuits

EDA Track

Kai-Chiang Wu and Diana Marculescu.

Power-Aware Soft Error Hardening via Selective Voltage Scaling

Verification and Test Track

Ilya Wagner and Valeria Bertacco.

Reversi: Post-Silicon Validation System for Modern Microprocessors

Session IV

Tuesday 10/14/08, 13:00-14:40

Logic and Circuits Track

Session 4.1 VLSI signal processing (100 minutes)

Session chair: Lars Svensson, Chalmers University

Jeong-Ho Han and In-Cheol Park.

Digital Filter Synthesis Considering Multiple Adder Graphs for a Coefficient

Adnan Suleiman, Hani Saleh, Adel Hussein and David Akopian.

A Family of Scalable FFT Architectures and an Implementation of 1024-point Radix-2 FFT For Real-Time Communications

Zhenyu Liu, Satoshi Goto and Takeshi Ikenaga.

Optimization of Propagate Partial SAD and SAD Tree Motion Estimation Hardwired Engine for H.264

Ali Namazi, Syed Askari and Mehrdad Nourani.

Highly Reliable A/D Converter Using Analog Voting

Verification and Test Track

Session 4.2 Simulation and Reliability (100 min)

Session chair: TBD

J.P. Grossman, John K. Salmon, C. Richard Ho, Douglas J. Ierardi, Brian Towles, Brannon Batson, Jochen Spengler, Stanley C. Wang, Rolf Mueller, Michael Theobald, Cliff Young, Joseph Gagliardo, Martin M. Deneroff, Ron O. Dror and David E. Shaw.

Hierarchical Simulation-Based Verification of Anton, a Special-Purpose Parallel Machine

Andrew DeOrio, Adam Bauserman and Valeria Bertacco.

Post-Silicon Verification for Cache Coherence

Christian Hochberger and Alexander Weiss.

Acquiring an Exhaustive, Continuous and Real-Time Trace from SoCs

Andrea Pellegrini, Kypros Constantinides, Dan Zhang, Shobana Sudhakar, Valeria Bertacco and Todd Austin.

CrashTest: A fast High-Fidelity FPGA-based Resiliency Analysis Framework

Processor Architecture Track

Session 4.3 Multi-Threaded and Multi-Core Architectures (100 min)

Session chair: Jarmo Takala, Tampere University of Technology

Jorg Mische, Sascha Uhrig, Florian Kluge and Theo Ungerer.

Exploiting Spare Resources of In-order SMT Processors Executing Hard Real-time Threads

Carsten Gremzow.

Quantitative Global Dataflow Analysis on Virtual Instruction Set Simulators for Hardware/Software Co-Design

(Short presentation)

Satyanarayana Nekkalapu, Haitham Akkary, Komalan Jothi, Renjith Retnamma and Xiaoyu Song.

A Simple Latency Tolerant Processor

(Short presentation)

Marius Grannaes, Magnus Jahre and Lasse Natvig.

Feedback Directed Prefetch Scheduling in CMPs

Arun Nair and Lizy Kurian John.

Simulation points for SPEC CPU 2006

Session V

Tuesday 10/14/08, 15:00-16:52

Logic and Circuits Track

Session 5.1 VLSI Arithmetic (112 minutes)

Session chair: Vojin Oklobdzija, UT Dallas

Taeko Matsunaga, Shinji Kimura and Yusuke Matsunaga.

Synthesis of parallel prefix adders considering switching activities

Ashur Rafiev, julian murphy, Danil Sokolov and Alex Yakovlev.

Conversion Driven Design of Binary to Mixed Radix Circuits

Atsushi Miyamoto, Naofumi Homma, Takafumi Aoki and Akashi Satoh.

Systematic design of high-radix Montgomery multipliers for RSA processors

Shai Erez and Guy Even.

An Improved Micro-Architecture for Function Approximation Using Piecewise Quadratic Interpolation

(Short presentation)

Hani Saleh and Earl Swartzlander.

A Floating-Point Fused Dot-Product Unit

EDA Track

Session 5.2 Modelling, Estimation and Simulation (112 min)

Session chair: TBD

Yufu Zhang, Ankur Srivastava and Mohamed Zahran.

Chip Level Thermal Profile Estimation Using On-chip Temperature Sensors

Shilpa Bhoj and Dinesh Bhatia.

Early Stage FPGA Interconnect Leakage Power Estimation

Aswin Sreedhar and Sandip Kundu.

Modeling and Analysis of Non-Rectangular Transistors Caused by Lithographic Distortions

Dimitrios Bountas, George Stamoulis and Nestoras Evmorfopoulos.

A macromodel technique for VLSI dynamic simulation by mapping pre-characterized transitions

(Short presentation)

Aditya Bansal, Rama Singh, Saibal Mukhopadhyay, Geng Han, Fook-Luen Heng and Ching-Te Chuang.

Pre-Si Estimation and Compensation of SRAM Layout Deficiencies to Achieve Target Performance and Yield

Computer Systems Track

Session 5.3 Multi-processor and Multi-core Systems (112 min)

Session chair: Hiroshi Nakamura

Michael Kadin and Sherief Reda.

Frequency and Voltage Planning for Multi-Core Processors Under Thermal Constraints

Nagesh Lakshminarayana and Hyesoon Kim.

Understanding performance, power and energy behavior in asymmetric processors

Michael Gschwind.

Optimizing Data Sharing and Address Translation for the Cell BE Heterogeneous Chip Multiprocessor

(Short presentation)

Reza Sabbaghi and Hamid Sarbazi-Azad.

The 2D DBM: An attractive Alternative to the Mesh Topology for On-chip Networks

(conditional accept)

Amit Hadke, Tony Benavides, Venkatesh Akella, Rajeevan Amirtharajah and Matthew Farrens.

Design and Evaluation of an Optical CPU-DRAM Interconnect

Conference Panel

Reset Microprocessor Hardware and Software Roadmaps for the next 30 Years?

Tuesday 10/14/08, 17:15-21:00

Organized by Reiner Hartenstein, Kaiserslautern University of Technology

More information can be found on the Conference Panel page.

Session VI

Wednesday 10/15/08, 8:30-10:10

Computer Systems Track

Session 6.1 Emerging Techniques (100 min)

Session chair: TBD

Computer Systems Track

Session 6.1 Emerging Techniques (100 min)

Session chair: TBD

Juan Carlos Martinez Santos and Yunsi Fei.

Leveraging Speculative Architectures for Run-time Program Validation

Michael Niemier, Aaron Dingler and X. Sharon Hu.

Bridging the Gap between Nanomagnetic Devices and Circuits

(Short presentation)

Christopher Nitta and Matthew Farrens.

Techniques for Increasing Effective Data Bandwidth

(Short presentation)

Hyotaek Shim, Jaegeuk Kim, Dawoon Jung, Jin-Soo Kim and Seungryoul Maeng.

RMA: A Read Miss-Based Spin-Down Algorithm using an NV cache

Jiangli Zhu, Xinmiao Zhang and Zhongfeng Wang.

Combined Interpolation Architecture for Soft-decision Decoding of Reed-Solomon Codes

EDA Track

Session 6.2 Timing (100 min)

Session chair: TBD

Shih-Hung Weng, Yu-Min Kuo, Shih-Chieh Chang and Malgorzata Marek-Sadowska.

Timing Analysis Considering IR Drop Waveforms in Power Gating Designs

(Short paper)

Sz-Cheng Huang and Jie Hong Jiang.

A Dynamic Accuracy-Refinement Approach to Timing-Driven Technology Mapping

Nagbhushan Veerapaneni and C Y Roger Chen.

Modeling and Reduction of Complex Timing Constraints in High Performance Digital Circuits

Anuj Kumar, Tai-Hsuan Wu and Azadeh Davoodi.

SynECO: Incremental Technology Mapping with Constrained Placement and Fast Detail Routing for Predictable Timing Improvement

(Short paper)

Yi-Wei Lin, Malgorzata Marek-Sadowska, Wojciech Maly, Andrzej Pfitzner and Dominik Kasprowicz.

Is There Always Performance Overhead for Regular Fabric?

Processor Architecture Track

Session 6.3 Energy-Efficiency and Security in Processor Designs (100 min)

Session chair: Eren Kursun, IBM

Houman Homayoun, Alex Veidenbaum and Jean-Luc Gaudiot.

Adaptive Techniques for Leakage Power Management in L2 Cache Peripheral Circuits

Balaji V. Iyer, Jason Poovey and Thomas M. Conte.

Energy-Aware Opcode Design

(Short presentation)

Shuo Wang, Fan Zhang, Jianwei Dai, Lei Wang and Zhijie Shi.

Making Register File More Resistant to Power Analysis Attacks

(Short presentation)

Shrirang Yardi and Michael Hsiao.

Quantifying the Energy Efficiency of Coordinated Micro-Architectural Adaptation for Multimedia Workloads

(Short presentation)

Christos Strydis.

Suitable cache organizations for a novel biomedical implant processor

(Short presentation)

Pedro Chaparro Monferrer, Jaume Abella, Javier Carretero Casado and Xavier Vera.

Issue System Protection Mechanisms

Session VII

Wednesday 10/15/08, 10:30-12:35

Logic and Circuits Track

Session 7.1 Low power (125 minutes)

Session chair: Amy Novak, AMD

Liang Di, Mateja Putic, Ben Calhoun and John Lach.

Power Switch Characterization for Fine-Grained Dynamic Voltage Scaling

Naomi Seki, Lei Zhao, Jo Kei, Daisuke Ikebuchi, Yu Kojima, Yohei Hasegawa, Hideharu Amano, Toshihiro Kashima, Seidai Takeda, Mitustaka Nakata, Kimivoshi Usami, Tetsuya Sunata, Jun Kanai, Mitaro Namiki, Masaaki Kondo, Hiroshi Nakamura and Toshiaki Shirai.

A Fine Grain Dynamic Sleep Control Scheme in MIPS R3000

Hao Xu, Ranga Vemuri and Wen-Ben Jone.

Run-time Active Leakage Reduction By Power Gating And Reverse Body Biasing: An Energy View

Michael Dayringer, Steven Huntzicker, Justin Soprano, Anthony Weerasinghe and David Harris.

Energy-Delay Tradeoffs in 32-bit Static Shifters

Baoxian Zhao, Hakan Aydin and Dakai Zhu.

Reliability-Aware Dynamic Voltage Scaling for Energy-Constrained Real-Time Embedded Systems

EDA Track

Session 7.2 Tools and Methodologies (125 min)

Session chair: Azadeh Davoodi, The University of Wisconsin

Feng Shi.

Removing Hazards in Multi-Level Logic Optimization for Generalized Fundamental-Mode Asynchronous Circuits

Wei-Chih Tseng, Yu-Hsiang Chen and Rung-Bin Lin.

Router and Cell Library Co-development for Improving Redundant Via Insertion at Pins

Nilesh Modi and Malgorzata Marek-Sadowska.

ECO-Map: Technology Remapping for Post-Mask ECO Using Simulated Annealing

Dae Hyun Kim and Sung Kyu Lim.

Global Bus Route Optimization with Application to Microarchitectural Design Exploration.

Giorgos Dimitrakopoulos, Nikos Chrysos and Kostas Galanopoulos.

Fast Arbiters for On-Chip Network Switches

Processor Architecture Track

Session 7.3 Cache Architectures (125 min)

Session chair: Brian Flachs, IBM

Jason Zebchuk, Srihari Makineni and Don Newell.

Re-Examining Cache Replacement Policies

Chuanjun Zhang.

Two Dimensional Highly Associative Level-Two Cache Design

Chungsoo Lim and Gregory T. Byrd.

Exploiting Producer Patterns and L2 Cache for Timely Dependence-based Prefetching

Sayaka Akioka, Feihui Li, Konrad Malkowski, Padma Raghavan, Mahmut Kandemir and Mary Jane Irwin.

Ring Data Location Prediction Schemes for Non-Uniform Cache Architectures

Houman Homayoun, Mohammad Makhzan and Alex Veidenbaum.

ZZ-HVS: Zig-Zag Horizontal and Vertical Sleep Transistor Sharing to Reduce Leakage Power in On-Chip SRAM Peripheral Circuits

The content and material posted on this web page represent solely the views and opinions of the ICCD conference.